Design challenges of PCIe Gen4 using Altium

FROM CONCEPT

TO MANUFACTURING

WWW.PCBDESIGN.HU

János Lazányi – CEO – PCB Design Kft.

CONSUMER • 5%

MEDICAL • 6%

INDUSTRIAL • 7%

AUTOMOTIVE • 7%

INFORMATION & COMMUNICATION TECH. • 34%

AEROSPACE & DEFENSE • 41%

DESIGN

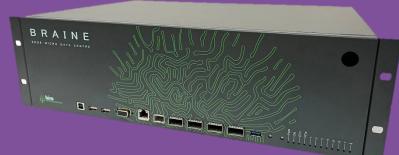

# **BRAINE** Project

Active contribution in various projects

- H2020, Horizon Europe

- ESA

- Cascaded funding (TETRAMAX, Smart4All)

- EDF

BRAINE: Big data Processing and Artificial Intelligence

at the Network Edge

H2020 ECSEL JU Grant No. 876967

https://www.braine-project.eu/

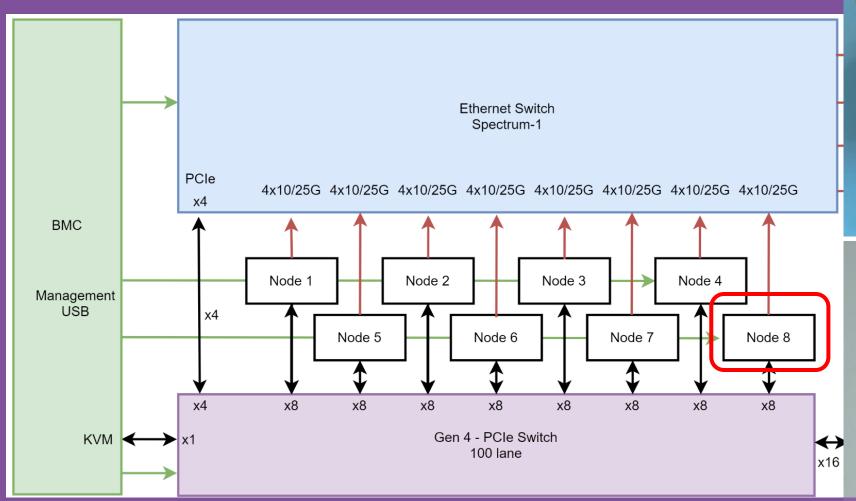

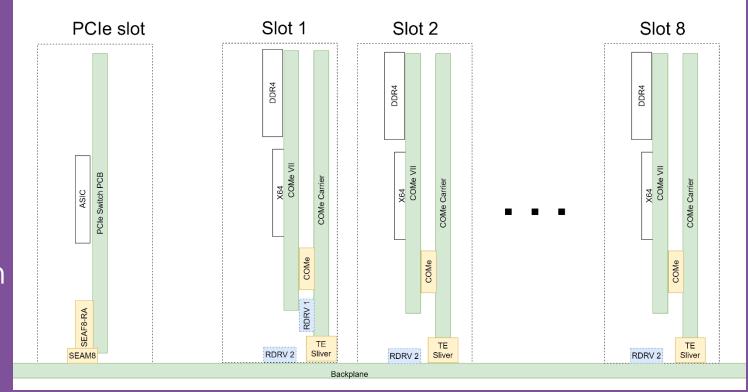

#### EMDC Edge Micro Data Center

3.2 TB/s Ethernet switch

3 kW PSU

3U Enclosure for 8 compute nodes

# 3U - Two phase cooled, 8/16/24 node EDGE /AI computer

#### **Technology**

- 1.5 kW / 8 node

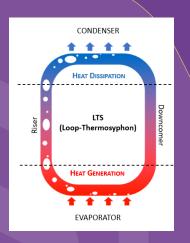

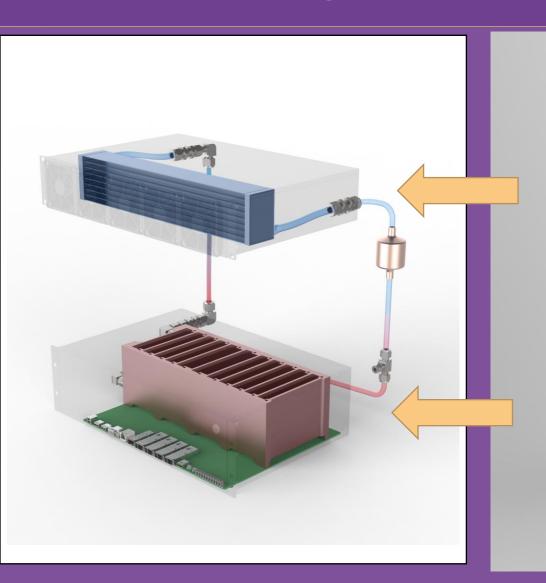

- Two phase passive cooling

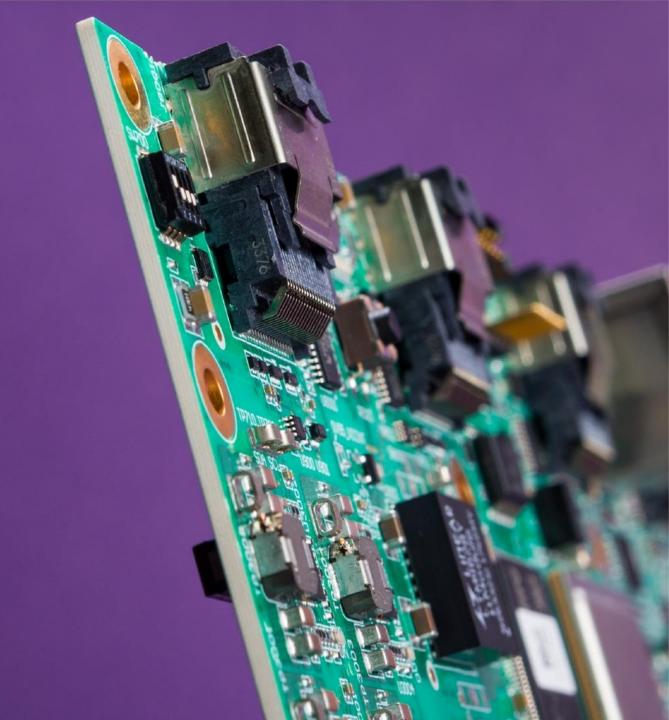

- Gen4 PCle switch fabric

- 3.2 TB/s Ethernet switching (32 x 100G)

- 24 compute nodes in 3U

- 48V operation

#### **Node types**

- COM Express (Type VII ) CPU

- NVIDIA Xavier/Orin GPU

- Xilinx Versal AI FPGA

- 64 core ARM

#### EMDC Edge Micro Data Center

**Condenser Unit**

Passive cooled

Reconfigurable

Server

(EMDC)

#### EMDC - Basic architecture

AMD Epyc CPU (COMe Type VII) www.pcbdesign.hu

## Switch components

#### **Ethernet switch**

- 128 x 25 G lane

- Mellanox / Spectrum 1

- 3.2 Tbit/sec switching

- 4x 100G External Ethernet

- 4x 25 G to each Node

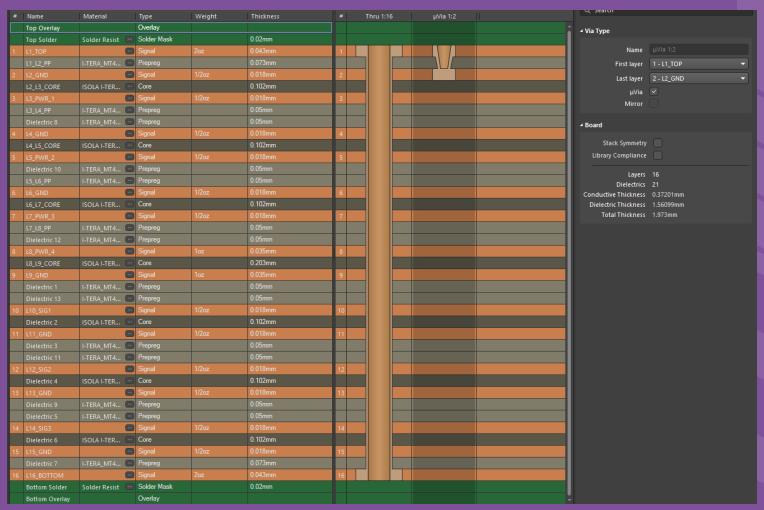

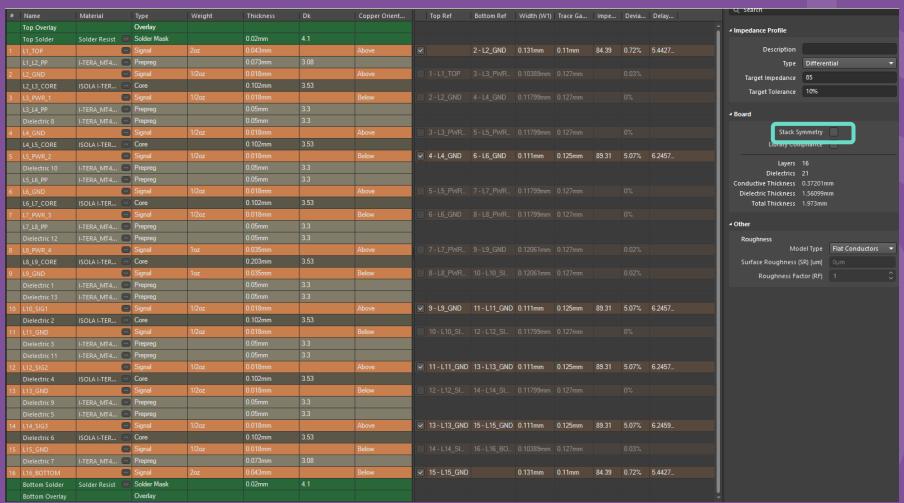

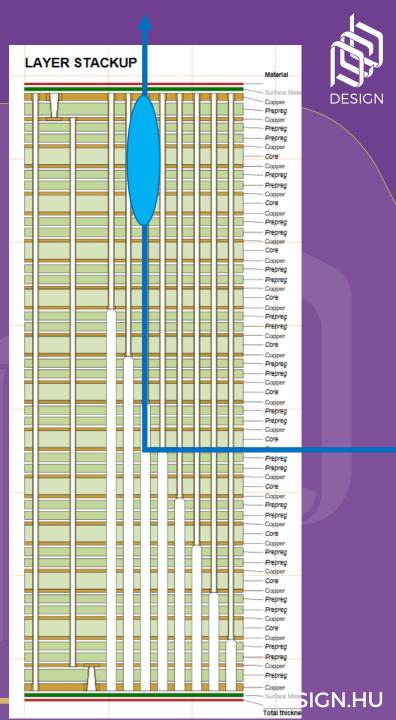

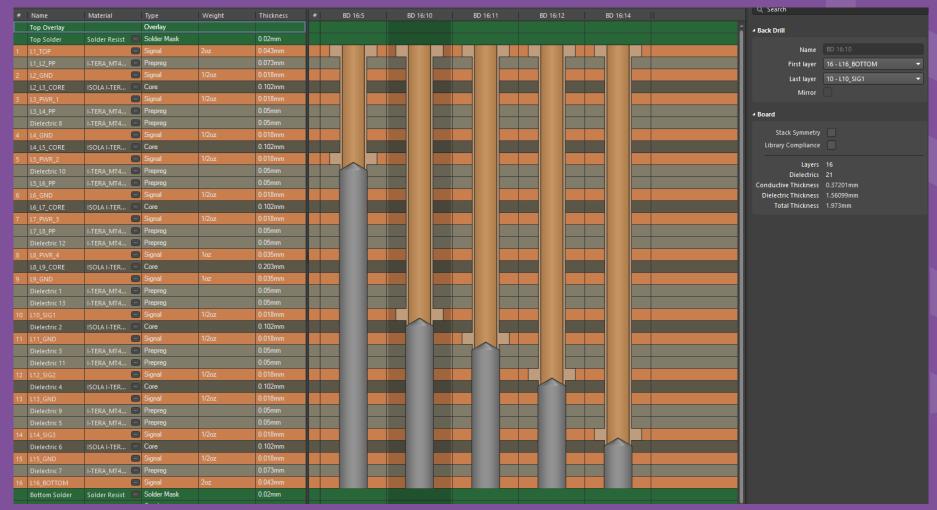

- 26 layer stackup

#### **PCIe Switch**

- 96 lane Gen 4 PCIe Switching

- Each node x8 interface

- 16 layer stackup

**Ethernet Switch**

PCIe Switch

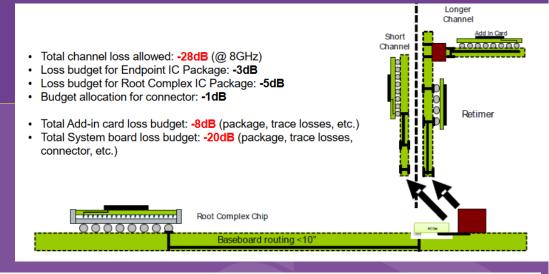

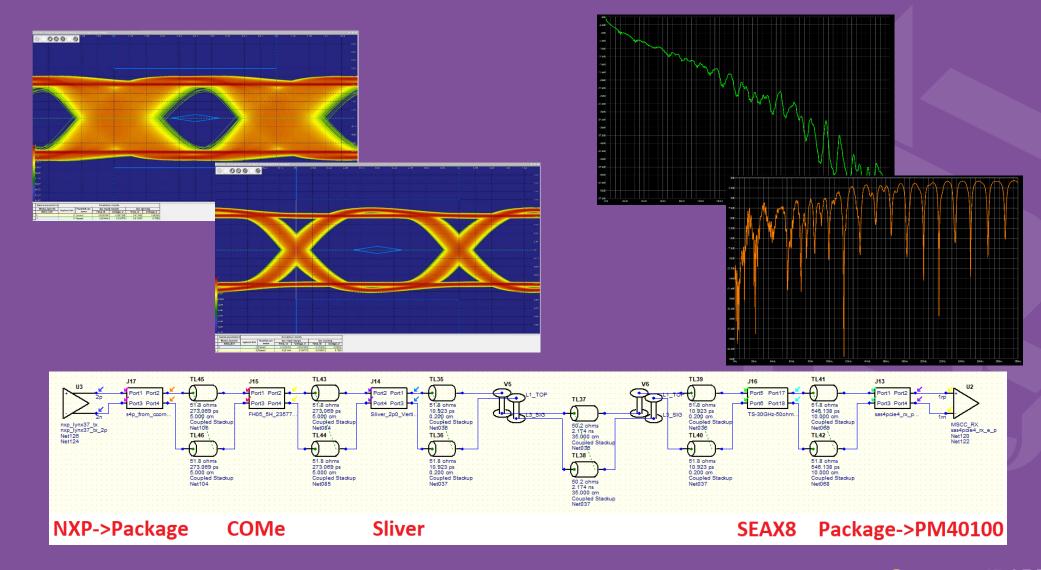

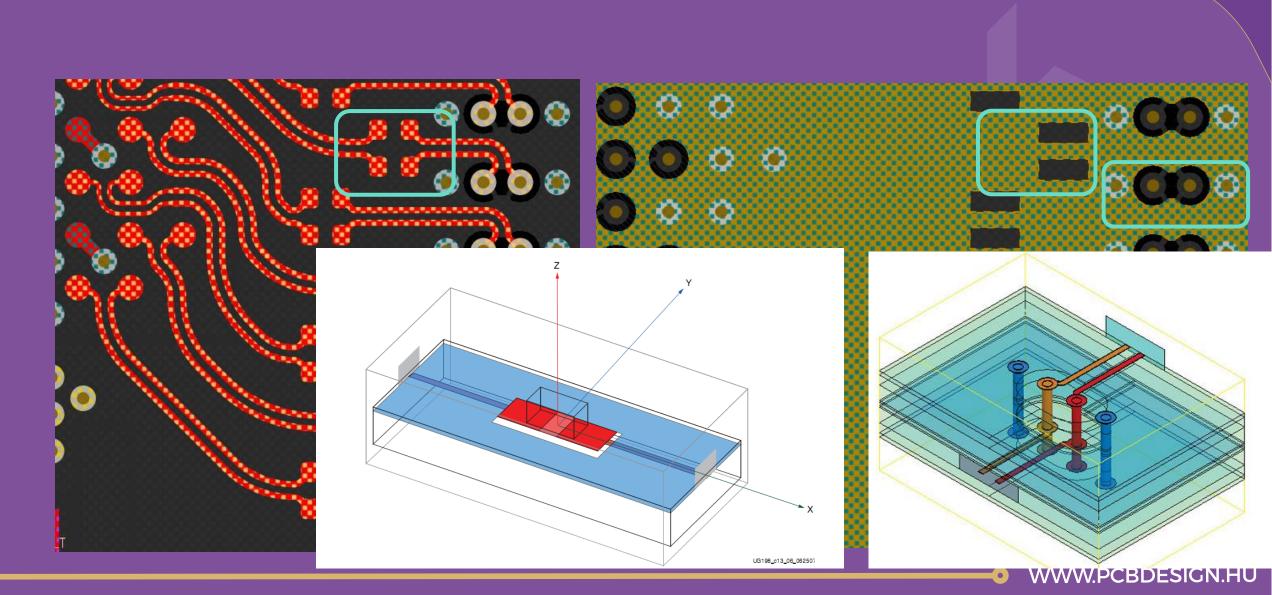

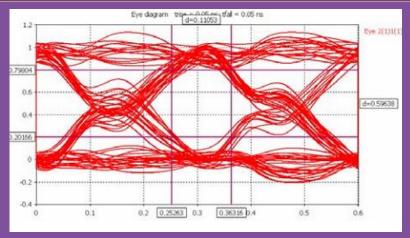

# Architectural simulations

#### Architecture simulations

Should work with all Node types

- Com Express Gen3

- GPU Gen 4

- Dual connectors

Slot- slot distance -Up to 300 mm

Connector Selection

PCB Material selection

-Channel Loss simulation

Re-driver required?

-If yes, where?

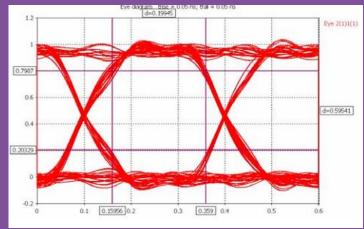

#### Simulation results

#### Conclusions

- Hard to find/trust simulation models

- Com Express?

- High Speed Material is required

MT40 was selected

- Backplane connector → ExaMax

- Re-timer/Repeater → Not required

- 12 dB loss @ 8 GHz

- If PCIe slot is in the middle

- "Universal" G-S-G structure stripline configuration

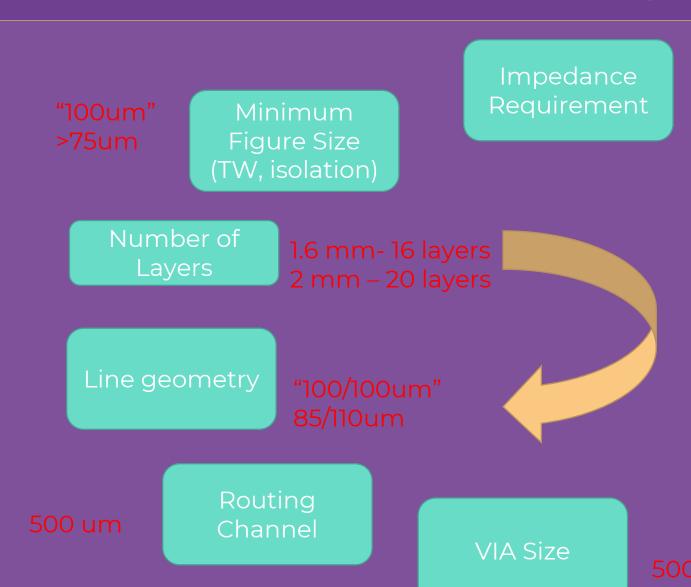

## Catch 22-High-Speed design parameters

VIA Size

Minimum Figure Size (TW, isolation)

Number of Layers

Line geometry

Routing Channel Impedance Requirement

> (Material type & thickness)

> > Total Thickness

Stackup

Aspect Ratio

Annual Ring IPC Class?

WWW.PCBDESIGN.HU

# High Speed design Losses & Impedance match

- Resistive losses

- Conductor DC resistance

- Skin depth

- Surface roughness -> HVLP material

- Dielectric loss

- Dielectric loss exceeds resistive loss around 3 Gbit/s

- Material selection (Df)

- Conductor geometry (Dk) Loss vs. routability

- Signal dispersion due to different relative propagation delay

- Df Stability

- Prep-preg construction

#### Stackup – VIA size

- Standard technology

- Through via + microvia if required

- No buried via if possible

- "Universal" G-S-G layer structure

- Signal layer count is not defined yet

- cca. 250 um (only) / signal layer

- MT40-Dk-3.3

|   | _                             |      | _      |

|---|-------------------------------|------|--------|

|   | $\Gamma_{\triangle} + \Delta$ | thia | kness  |

| _ | Cla                           |      | KIIUSS |

- Required number of signal (+power) layers

- If exceeding 1.6 mm

- Card edge connector (Standard PCIe problem) → No problem here

- If exceeding 2 mm

- Pin length -> Press fit -> No problem

- Aspect ratio 1:8 max 1:10

- Results VIA size constraints

| 13 | L13_GND      | -                   | Signal  | 0.018mm |

|----|--------------|---------------------|---------|---------|

|    | Dielectric 9 | I-TERA_MT40-103     | Prepreg | 0.05mm  |

|    | Dielectric 5 | I-TERA_MT40-103 ••• | Prepreg | 0.05mm  |

| 14 | L14_SIG3     |                     | Signal  | 0.018mm |

|    | Dielectric 6 | ISOLA I-TERA MT     | Core    | 0.102mm |

| 15 | L15_GND      |                     | Signal  | 0.018mm |

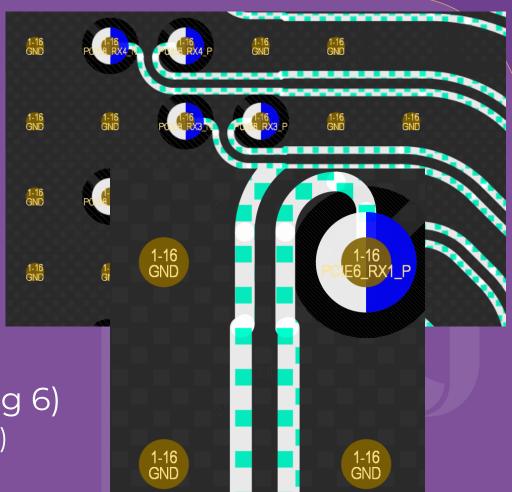

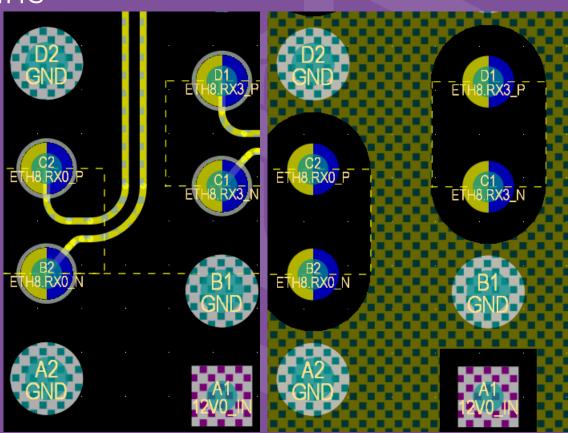

#### Fanout

- 1 mm BGA pitch

- Diff line fanout

- 1mm routing channel

- 500 um PAD Size

- 250 um drill size

- 1:8 Aspect ratio @ 2mm PCB

- 1:10 Aspect ratio @ 2.5mm PCB

- 2 x 125 um annual ring

- 500 um Routing channel MT40(Meg 6)

- Ideally 5x 100um (2 Signal + 3 separation)

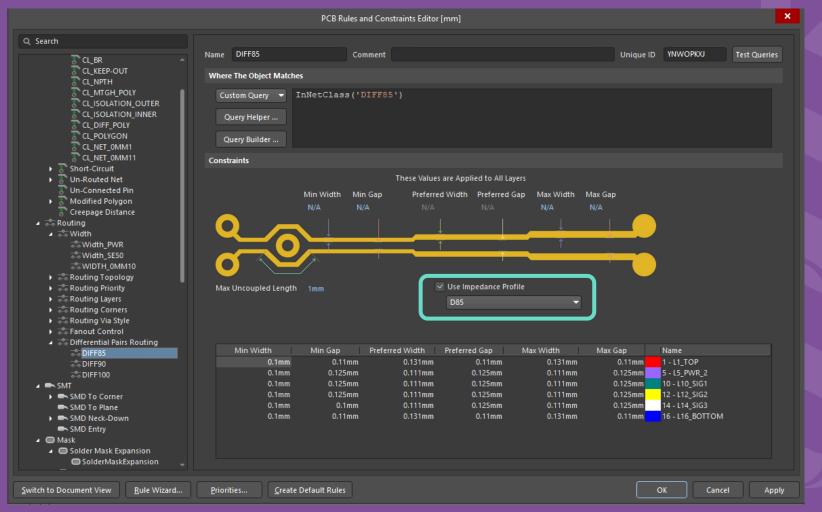

- DIFF 100: 85 um SIG + 0.11 GAP

- DIFF 85: 110um SIG + 125 um GAP

- results 77 um drill to track

- neckdown

77 + (110 + 125 + 110) + 77

# Catch 22 – Solution for High-Speed designs

Stackup (Material type MT40 & thickness) Megtron 6 1.6 mm Total 2 mm Thickness 2.5 mm 3 mm Aspect Ratio **Annual Ring** IPC Class?

WWW.PCBDESIGN.HU

# Minimize impedance mismatch

## Impedance - VIA setup

Stackup and VIA settings

## Impedance - VIA setup

• Impedance table

## Impedance - VIA setup

• Impedance – net class, rule

# Advanced topics

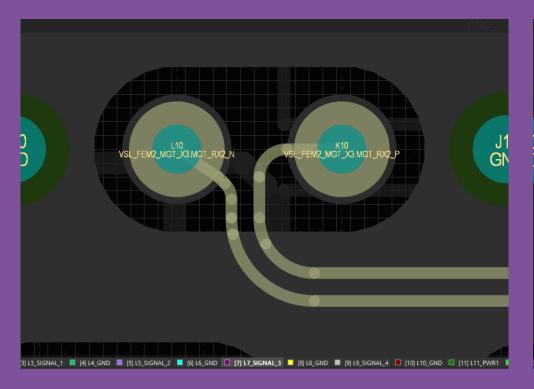

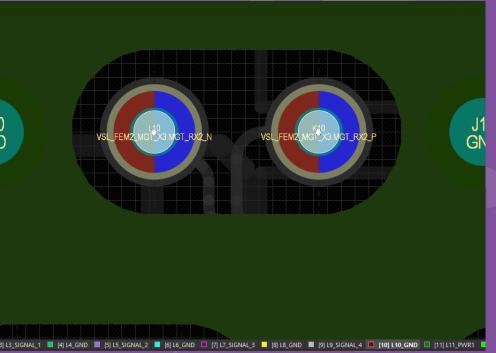

#### Additional items to consider

- Examax routing

- Antipad design

- Length equalization wo. serpentine

- Backdrill depth limit

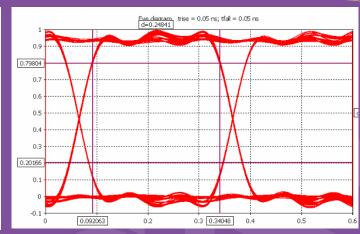

# Back drilling -stub effect

No Stub

3.3 mm Stub

- 16 layer PCB

- VIA L1-L2

- 50ps rise/fall time

- 300ps pulse

#### Additional items to consider

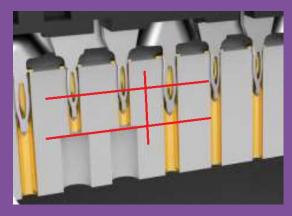

Press-fit + drill tolerance limitation

- Topmost layers still suffer from stub

- Altium does not recognize press fit

# Backdrill setup in Altium

Automatically generated after setup

## Backdrill setup in Altium

- Small feature to stop backdrill at press-fit.

- Signal is routed on L7 -> backdrill would be automatically generated from bottom to L7.

- Solution: add a small track to L10

#### Additional items to consider

- Crosstalk mitigation

- Guard ring around the signals.

- VIA in PAD required.

- IPC 4761 VII Filled & Capped via

WWW.PCBDESIGN.HU

3 days training @ Budapest: 08 - 10 / March 2023